# Heterogeneous Integrated Microsystems With Nontraditional Through-Silicon Via Technologies

Hanju Oh, *Student Member, IEEE*, Gary S. May, *Fellow, IEEE*, and Muhannad S. Bakir, *Senior Member, IEEE*

(Invited Paper)

**Abstract**—In this paper, the design, fabrication, and high-frequency characterization of three types of nontraditional through-silicon via (TSV) technologies are discussed. First, the integration of TSVs within a silicon microfluidic heat sink is presented; TSVs are fabricated within a pin-fin heat sink, and the frequency response of TSVs within a deionized-water-filled silicon pin-fin heat sink is experimentally analyzed. Second, to electrically shield the signal transmission of such TSVs, coaxially shielded TSVs consisting of multiple ground TSVs surrounding a single signal TSV are demonstrated. It is experimentally shown that as the number of ground TSVs increases, shielding is improved. Finally, a partial air-isolation technique is proposed to reduce TSV loss and capacitance at high frequencies.

**Index Terms**—3-D microsystem, air isolation, coaxial through-silicon via (TSV), microfluidic cooling, microfluidic pin-fin, packaging, silicon microsystem.

## I. INTRODUCTION

DEMAND for high-bandwidth communication with low energy consumption continues to grow in modern computing systems [1], [2]. Through innovations in materials, processes, and structures, integrated circuit technology has rapidly evolved—transistor count has increased by a factor of 16 000, and gate speed has increased by a factor of 100 since the mid-1980s [2], [3]. Along with such efforts, the need for revolutionary innovation in system integration has become necessary to overcome the limitations of traditional packaging [4]. Moreover, chip-to-chip communication has emerged as a key bottleneck that limits total system performance. To address these needs, heterogeneous integrated microsystems in which multiple (and differing) dice are integrated within a single package have been proposed [5], [6]. Some of the proposed integrated microsystems include the vertical stacking of dice, i.e., 3-D integration, and the side-by-side bonding of chips on a substrate with dense interconnects, termed 2.5-D integration.

Manuscript received August 22, 2016; revised December 29, 2016; accepted February 9, 2017. Date of publication March 29, 2017; date of current version April 18, 2017. Recommended for publication by Associate Editor S. G.-Talocia upon evaluation of reviewers' comments.

The authors are with the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA 30318 USA (e-mail: hanju.oh@gatech.edu; gary.may@coe.gatech.edu; muhannad.bakir@mirc.gatech.edu).

Color versions of one or more of the figures in this paper are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/TCMPT.2017.2678461

Through-silicon vias (TSVs) are a key enabler for stacked microsystems, providing vertical interconnection between stacked dice. The advantages of TSVs include high-bandwidth communication with greatly reduced routing lengths between dice. Moreover, they contribute to system miniaturization by geometrically integrating dice within the same footprint. For these reasons, TSV technology has been adopted in a number of applications that include CMOS image sensors (CISs), which are representative high volume-manufactured application [7], [8]. In addition, the dynamic random access-memory (DRAM) market continues to showcase the adoption of TSV technology in high-bandwidth memory [9], Wide-I/O DRAM [10], and hybrid memory cube [11] microsystems.

From the above-mentioned discussion, it is clear that TSV technology has been the focus of significant recent research, including studies that seek to improve the electrical and/or thermomechanical performance of TSVs by including atypical materials in a CMOS process flow or atypical configurations. In this paper, we refer to such TSVs as nontraditional TSVs. First, the integration of microfluidic cooling with TSVs has been proposed for various heterogeneous integrated microsystems [12]–[19]. Thermal management is one of the critical issues for 3-D integrated microsystems because they can exhibit relatively large heat flux [20]. With its effective cooling capability, microfluidic cooling has been explored as a promising solution to heat rejection. Recently, the monolithic integration of microfluidic cooling on the back side of a field-programmable gate array has been demonstrated, and measurements suggest improved performance compared to air cooling [13]. Moreover, coaxial TSV configurations have been explored to electrically shield signal vias from the surrounding medium [21]–[26]. A coaxial TSV structure consists of a center core via surrounded by an outer ground conductor. To fabricate this TSV configuration, several approaches have been explored, including polymers defined by photolithography [21], [24], organic material defined by laser ablation [22], [23], and silicon dioxide deposited by subatmospheric chemical vapor deposition (SACVD) [25]. Finally, low-loss TSV technologies have been explored to reduce electrical loss and capacitance resulting from a lossy silicon substrate. Various loss reduction techniques have been proposed, such as low-*k* liners, increased liner thickness [27], glass substrate [28], a localized

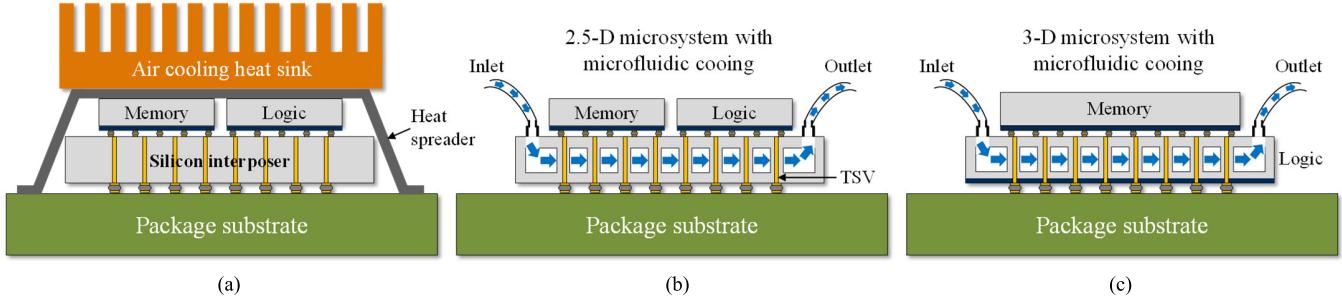

Fig. 1. Three types of heterogeneous integrated microsystems. (a) 2.5-D integration using silicon interposer with conventional air cooling technology. (b) 2.5-D integration using silicon interposer with embedded microfluidic cooling technology. (c) 3-D microsystem with embedded microfluidic cooling technology.

TABLE I

COMPARISON OF TSVs INTEGRATED WITH MICROFLUIDIC COOLING TECHNOLOGY

| Parameters                       | C. R. King <i>et al.</i><br>[12] | Y. Madhour <i>et al.</i><br>[15]            | N. Khan <i>et al.</i><br>[17]              | Y. Zhang <i>et al.</i><br>[18]          | H. Oh <i>et al.</i><br>[19]              |

|----------------------------------|----------------------------------|---------------------------------------------|--------------------------------------------|-----------------------------------------|------------------------------------------|

| TSV diameter                     | 50 $\mu\text{m}$                 | 60 $\mu\text{m}$                            | 150 $\mu\text{m}$                          | 13 $\mu\text{m}$                        | 13 $\mu\text{m}$                         |

| TSV height                       | $\sim$ 300 $\mu\text{m}$         | 380 $\mu\text{m}$                           | 400 $\mu\text{m}$                          | 300 $\mu\text{m}$                       | 320 $\mu\text{m}$                        |

| TSV pitch                        | 200 $\mu\text{m}$                | $\sim$ 200 $\mu\text{m}$                    | 500 $\mu\text{m}$                          | 24 $\mu\text{m}$                        | 200 $\mu\text{m}$                        |

| Heat sink type                   | Channel                          | Channel                                     | Channel                                    | Pin-fin                                 | Pin-fin                                  |

| Heat sink width<br>(or diameter) | 100 $\mu\text{m}$                | 100 $\mu\text{m}$                           | 50 $\mu\text{m}$                           | 150 $\mu\text{m}$<br>(diameter)         | 50, 100, 150 $\mu\text{m}$<br>(diameter) |

| Heat sink height                 | 200 $\mu\text{m}$                | 100 $\mu\text{m}$                           | 175 $\mu\text{m}^*$                        | 200 $\mu\text{m}$                       | 220 $\mu\text{m}$                        |

| Note                             | Long microchannel used           | Vertical stack of 5 chips using solder bond | TSVs are not fabricated inside a heat sink | 16 TSVs fabricated in each micropin-fin | TSV pitch is fixed for all diameters     |

\*Two wafers are face-to-face bonded, so it gives a total height of 350  $\mu\text{m}$ .

polymer-well [29] or glass-well in a silicon substrate [30], and the formation of air within a substrate [31]–[33].

This paper discusses some of the aforementioned nontraditional TSV configurations, including their design, fabrication, and high-frequency measurements. In Section II, the integration of TSVs with microfluidic cooling is discussed. Section III presents coaxially shielded TSVs, which consist of multiple ground TSVs surrounding a signal TSV, benchmarked to other coaxial TSV technologies. Moreover, this section investigates the optimal number of ground TSVs to sufficiently shield a signal TSV. In Section IV, this paper discusses loss reduction techniques for TSVs in a silicon substrate.

## II. TSVS INTEGRATED WITH MICROFLUIDIC COOLING

Fig. 1 illustrates three heterogeneous integrated microsystems with two cooling technologies (air and microfluidic). In Fig. 1(a), the logic and the memory dice are bonded side-by-side in a 2.5-D configuration with an air-cooled heat sink. Fig. 1(b) illustrates the integration of microfluidic cooling within a silicon interposer. Because microfluidic cooling offers a number of benefits compared to air cooling, significant reduction in junction temperature is expected in such systems. Fig. 1(c) illustrates a heterogeneous 3-D microsystem in which logic and memory dice are stacked on top of each other, with integrated microfluidic cooling. Such a 3-D stack can further improve bandwidth, latency, and I/O power because it provides the shortest interconnect lengths between chips. However, the 3-D stack has the highest integration complexity among the microsystems in Fig. 1.

Table I summarizes the specifications of TSVs integrated within microfluidic cooling technologies in the literature. One general challenge of such TSV integration is that it necessitates TSVs to be fabricated inside a microfluidic heat sink, and this introduces several fabrication challenges. From a cooling perspective, a relatively “thick” die is preferred since the height of a microfluidic heat sink is related to its cooling capability (thermal resistance) [16]. However, this inevitably requires TSVs to be relatively tall. For this reason, the height of most TSVs in Table I is more than 300  $\mu\text{m}$ . On the other hand, from an electrical point of view, it is desired to have as small an allocation of copper as possible for TSVs in a silicon substrate. This is because the area allocated to copper TSVs directly consumes active circuit area. Moreover, as the diameter of TSVs increases, not only does electrical TSV capacitance increase, but thermomechanical stress also increases [34]. However, it should be noted that the diameter of TSVs cannot be boundlessly reduced since this will dramatically increase fabrication complexity, such as silicon etching and copper filling. Thus, it is critical to maximize the aspect ratio of TSVs without increasing fabrication complexity to satisfy both electrical and cooling metrics.

### A. Fabrication of TSVs Embedded in a Silicon Microfluidic Heat Sink

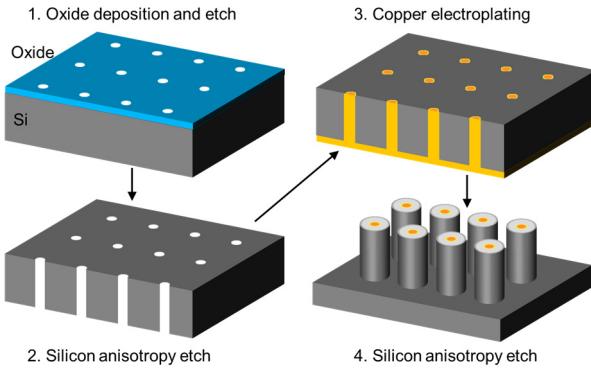

Fig. 2 summarizes the fabrication process for TSVs embedded in a silicon microfluidic heat sink. The fabrication begins with the deposition of silicon dioxide followed by an anisotropic dry etch of the deposited oxide. Using the etched

Fig. 2. Fabrication process of TSVs embedded in a silicon microfluidic pin-fin heat sink.

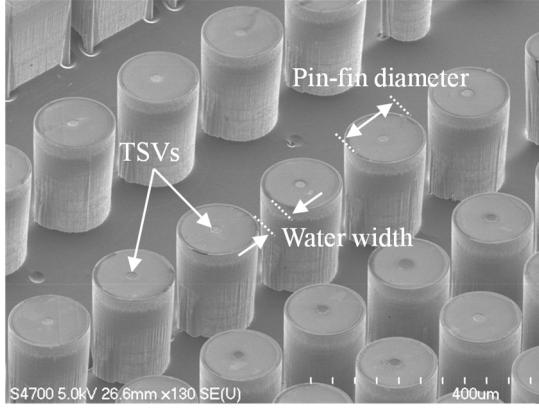

Fig. 3. SEM image of microfluidic pin-fins with embedded TSVs: Each pin-fin contains one TSV [19].

oxide as an etch mask, vias are etched in the silicon wafer using a deep reactive-ion etching process. After removing the remaining oxide, the wafer is placed in a thermal furnace at 1100 °C to form an oxide liner. Following thermal oxidation, electroplating is performed through three steps. First, a titanium and copper seed layer is deposited using an e-beam evaporator on the back side of the wafer. Second, dc electroplating is performed using an Enthone MICROFAB DVF electroplating solution to pinchoff the etched holes at the back side of the wafer. Next, a bottom-up electroplating process is performed to fill the etched holes with copper. After electroplating, removal of the excess copper is accomplished using chemical mechanical polishing (CMP) on both sides of the wafer. Finally, a circular microfluidic pin-fin structure is fabricated using the Bosch process, as shown in Fig. 3.

#### B. Frequency Response of TSVs With the Presence of Deionized Water

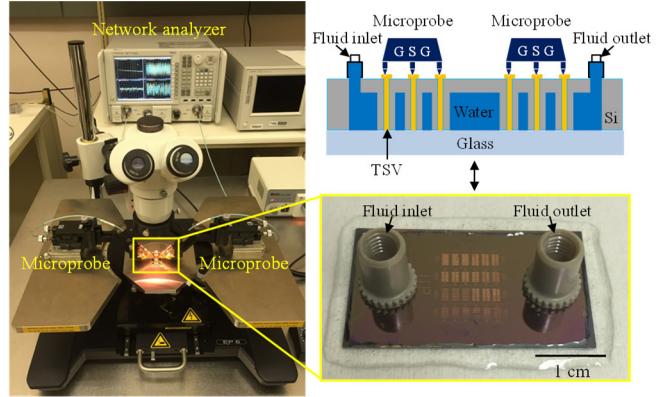

To evaluate the frequency response of TSVs in the presence of deionized (DI) water, the test bed is bonded (i.e., capped) to a glass wafer (to enable visualization) and filled with DI water, as shown in Fig. 4(a). To remove any undesirable conductivity in the DI water (such as ions), DI water with a conductivity of less than 0.5  $\mu\text{S}/\text{m}$  and dissolved solid concentration of less than 0.5 ppm is chosen for the experiments.

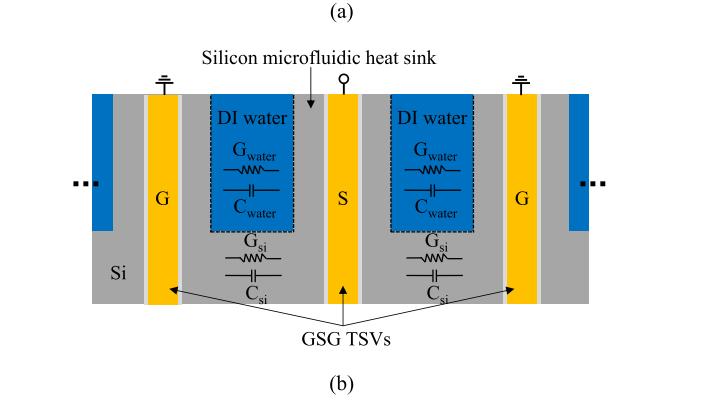

Fig. 4. (a) Measurement setup for the high-frequency characterization of the silicon pin-fin TSV testbed filled with DI water. (b) Schematic of GSG TSVs embedded in a silicon microfluidic pin-fin heat sink in the presence of DI water.

The high-frequency characterization of ground-signal-ground (GSG) TSVs is performed using microprobes and a network analyzer in the frequency range of 10–20 GHz. Prior to the measurements, short-open-load-through calibration is carried out on a calibration substrate. As shown in Fig. 4(b), there is a capacitive path partially through the DI water and the silicon between TSVs, and thus the frequency response of the GSG TSVs in the test bed is the aggregate S-parameters that include the electrical properties of both silicon and DI water.

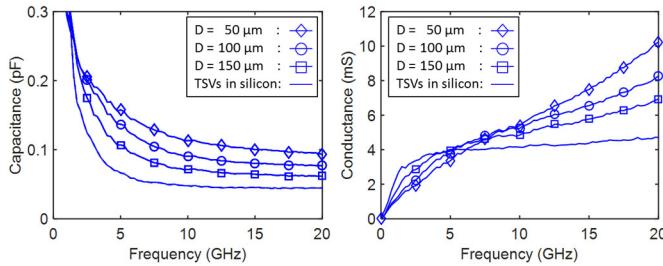

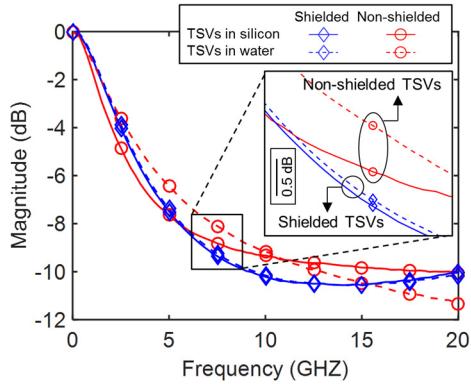

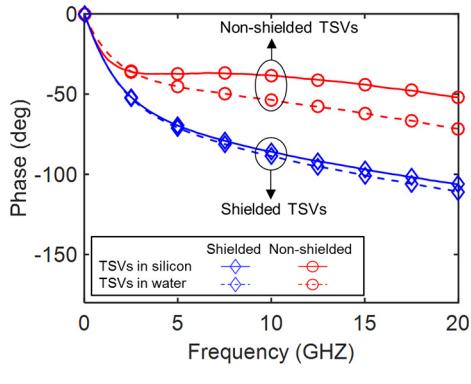

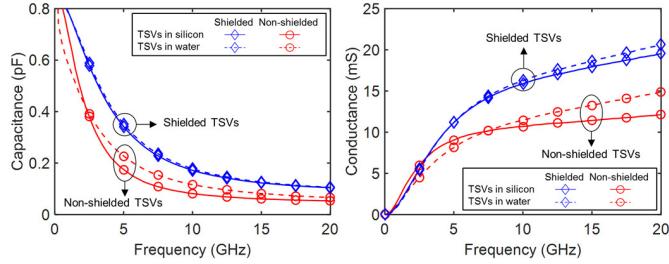

Given that the permittivity of DI water varies from 78–11.5 in the frequency band of 1.8–57.8 GHz [35], this frequency-dependent permittivity of DI water may cause a large variation in TSV frequency response as a result of variations in TSV capacitance and conductance. First, the capacitance and conductance of TSVs in silicon are analyzed as a reference for our TSVs embedded in silicon pin-fins with DI water. As discussed in the literature [36], [37], the capacitance of TSVs is dominated by oxide capacitance at low frequency and saturates to the substrate (silicon) capacitance, as shown in Fig. 5 (left). Similarly, the conductance of TSVs is dominated by oxide conductance, which is nearly zero, at low frequency and saturates to the substrate (silicon) conductance, as shown in Fig. 5 (right). For the TSVs in silicon pin-fins with DI water, TSV capacitance is dominated by oxide capacitance at low frequency (similar to TSVs in silicon). However, at high frequencies, TSV capacitance is saturated

TABLE II

COMPARISON OF NONTRADITIONAL COAXIAL TSVs IN THE LITERATURE

| Parameters            | S. W. Ho <i>et al.</i><br>[21]             | P. Thadesar <i>et al.</i><br>[24]                | D. H. Jung <i>et al.</i><br>[22]                   | J.-M. Yook <i>et al.</i><br>[23]                  | S. Adamshick <i>et al.</i><br>[25]                 | H. Oh <i>et al.</i><br>[26]                 |

|-----------------------|--------------------------------------------|--------------------------------------------------|----------------------------------------------------|---------------------------------------------------|----------------------------------------------------|---------------------------------------------|

| TSV diameter          | 100 $\mu\text{m}$                          | 65 $\mu\text{m}$                                 | 30/42 $\mu\text{m}$<br>(inner/outer)               | 70 $\mu\text{m}$                                  | 5 $\mu\text{m}$                                    | 13 $\mu\text{m}$                            |

| TSV height            | 300 $\mu\text{m}$                          | 285 $\mu\text{m}$                                | 205 $\mu\text{m}$                                  | 150 $\mu\text{m}$                                 | 50 $\mu\text{m}$                                   | 320 $\mu\text{m}$                           |

| Insulator material    | SU-8                                       | SU-8                                             | ABF*                                               | ABF                                               | Silicon dioxide                                    | Silicon dioxide                             |

| Insulator thickness   | 500 $\mu\text{m}$                          | 125/150 $\mu\text{m}$<br>(TSV pitch)             | 25 $\mu\text{m}$                                   | 20 ~ 120 $\mu\text{m}$<br>(20 $\mu\text{m}$ step) | 0.5 $\mu\text{m}$                                  | 50/100 $\mu\text{m}$<br>(TSV pitch)         |

| Coaxial TSV formation | Photolithography                           | Photolithography                                 | Laser ablation                                     | Laser ablation                                    | SACVD oxide                                        | Silicon etch<br>(Bosch process)             |

| Note                  | RO4350B substrate used for the bottom chip | Multiple ground TSVs (instead of annular ground) | Two metal layers at top and bottom (sig. and gnd.) | High-R silicon substrate used for the bottom chip | Two metal layers at top and bottom (sig. and gnd.) | Isolation of TSVs from surrounding DI water |

\*ABF stands for Ajinomoto build-up film ( $\epsilon_r = 3.7$  and  $\tan\delta = 0.01$ ).

Fig. 5. Extracted capacitance and conductance from measurements. ( $D$ : the diameter of microfluidic pin-fins [19]. As  $D$  increases, spacing between the pin-fins is reduced.)

to the aggregate capacitance of both silicon and the high-permittivity DI water.

To quantitatively analyze this behavior, our test bed contains three pin-fin heat sink diameters (50, 100, and 150  $\mu\text{m}$ ) at a fixed TSV pitch of 200  $\mu\text{m}$ . In other words, the width of the water region between the silicon pin-fins is 150, 100, and 50  $\mu\text{m}$ , respectively, as shown in Fig. 3 (note, as the spacing increases, so does the volume of DI water between the signal/ground TSVs). Moreover, the test bed contains TSVs in a silicon substrate without any pin-fin structures as a reference. TSV capacitance and conductance are extracted from the measured S-parameters and shown in Fig. 5. As the diameter of pin-fins decreases, or equivalently the width of DI water region increases, TSV capacitance increases. This is due to the high permittivity of DI water compared to the permittivity of silicon. At 20 GHz, the capacitance of TSVs in microfluidic pin-fins with DI water is 91.5, 76.9, and 62.0 fF when the diameter of the pin-fins is 50, 100, and 150  $\mu\text{m}$ , respectively; the capacitance of TSVs in silicon is 44.76 fF. However, the measured TSV conductance shows the opposite behavior at low- and high-frequency ranges. At a low-frequency range, TSV conductance decreases as the volume of DI water between TSVs increases, or the diameter of pin-fin decreases. At a high-frequency range, TSV conductance increases as the volume of water increases. At 20 GHz, the conductance

is 10.4, 8.3, and 6.9 mS when the diameter of the pin-fins is 50, 100, and 150  $\mu\text{m}$ , respectively, and TSV conductance is 4.7 mS for the reference TSVs in silicon.

### III. COAXIALLY SHIELDED TSVs WITHIN A MICROFLUIDIC PIN-FIN HEAT SINK USING A COAXIAL CONFIGURATION

As discussed in Section II, the frequency-dependent permittivity of DI water significantly impacts the electrical characteristics of GSG TSVs. To mitigate this issue, this section discusses electrically shielded TSVs for liquid-cooled microsystems. In general, to shield undesirable noise or coupling, a coaxial configuration is utilized. For integrated microsystems, coaxial TSVs have been proposed to shield vertical signal transmission in a silicon substrate [21]–[26], as summarized in Table II. The coaxial TSVs show good shielding performance, as well as reduced noise and loss. However, they face a number of fabrication challenges. First, the fabrication of a coaxial structure requires additional materials or processes, such as SU-8 [21], [24], ABF [22], [23], or oxide using SACVD [25]. Moreover, the outer ground conductor of the coaxial TSVs is typically larger in area than the center signal TSV. This is because the ground conductor is annular, while the signal via is circular; this geometry and size mismatch increases fabrication complexity in the Bosch process as well as in electroplating.

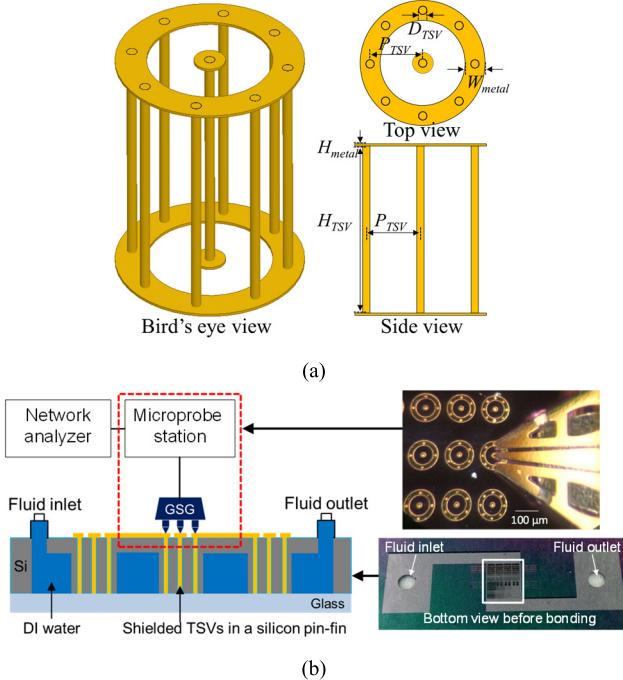

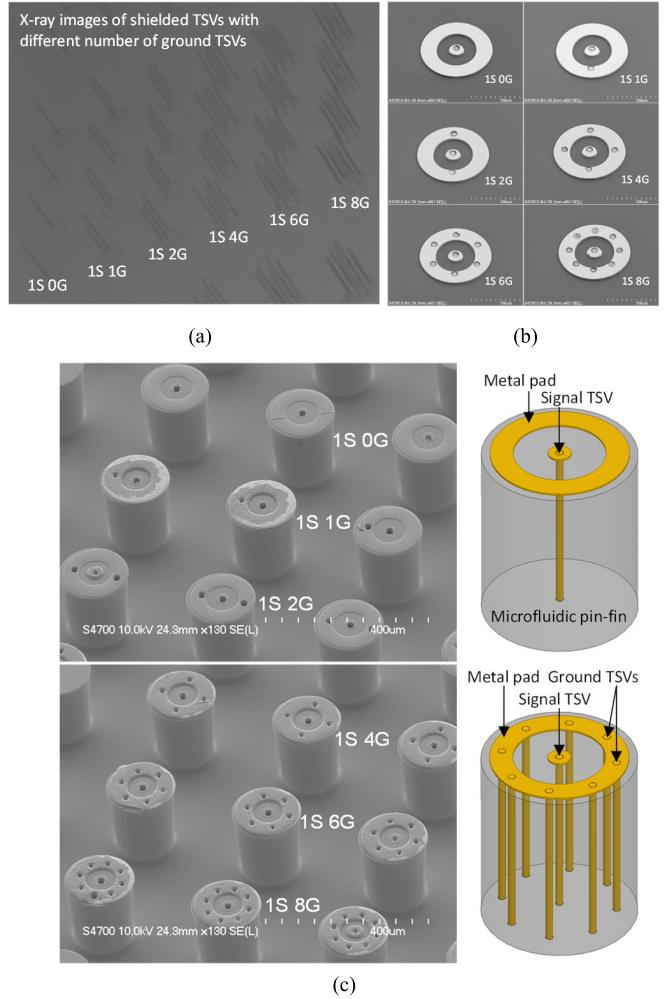

To address these challenges without increasing fabrication complexity, this section describes a coaxial-like concept to shield a signal TSV by placing multiple ground TSVs (instead of an annular conductor) around the center signal TSV, as shown in Fig. 6(a). Such an approach enables the wafer-level batch fabrication of signal and ground TSVs simultaneously. Fig. 6 illustrates the layout and measurement setup of coaxially shielded TSVs with their dimensions. It is expected that there is an optimal number of ground TSVs to sufficiently shield the signal TSV. To analyze this behavior, the coaxially shielded TSVs in the test bed consist of a number of ground TSVs (0, 1, 2, 4, 6, and 8). Fig. 7(a) shows an X-ray image of coaxially shielded copper TSVs with a varying number of

Fig. 6. (a) Layout of the coaxially shielded TSVs using multiple (0, 1, 2, and 8) ground TSVs:  $D_{TSV} = 13 \mu\text{m}$ ,  $H_{metal} = 3 \mu\text{m}$ ,  $H_{TSV} = 320 \mu\text{m}$ ,  $W_{metal} = 20 \mu\text{m}$ , and  $P_{TSV} = 50$  and  $100 \mu\text{m}$ . (b) Measurement setup for the high-frequency characterization of the TSV test bed filled with DI water.

ground TSVs. To facilitate probing, annular-shaped metal pads are selectively deposited to short all ground TSVs, as shown in Fig. 7(b).

To investigate the frequency response of the coaxially shielded TSVs, the fabricated test bed is bonded to a glass substrate (to encapsulate the fluidic passages) and filled with DI water, as illustrated in Fig. 6(b). In our high-frequency measurements, single-port characterization is performed since TSV capacitance and conductance can be directly extracted from a scattering matrix [36], [37]. In this paper, we focus on evaluating the variation in terms of the magnitude and phase of the scattering matrix for the shielded and nonshielded TSVs. Fig. 8 illustrates the measured  $S_{11}$  values for both the shielded and nonshielded TSVs. For each case, two sets of measurements are performed in the following manner. First, we measure the S-parameters of the TSVs in a silicon substrate ("TSVs in silicon" in Fig. 8). Next, we perform another measurement for the TSVs within a microfluidic pin-fin heat sink surrounded by DI water ("TSVs in water" in Fig. 8). For the nonshielded TSV case, a maximum of 1.46 dB difference is found between TSVs in silicon and the TSVs in microfluidic pin-fins with water. However, for the shielded TSVs, the magnitude difference was suppressed to 0.08 dB, and the phase variation was also significantly suppressed. The capacitance and conductance of TSVs in both cases are extracted from the measurements, as shown in Fig. 9. The results show a maximum difference of 0.14 pF in capacitance and 2.75 mS in conductance for nonshielded TSVs, while these are reduced to 0.02 pF and 1.12 mS, respectively, with the shield TSVs. This clearly indicates that signal transmission in the shielded TSVs is mostly isolated despite the presence of DI water.

Fig. 7. (a) SEM images of TSVs with the metal pad connecting ground TSVs (a front side view). (b) X-ray images of a TSV array with different numbers of ground TSVs (0, 1, 2, 4, 6, and 8 ground TSVs). (c) Schematics and SEM images of microfluidic pin-fins with different number of ground TSVs (a back side view). A signal TSV is located at the center surrounded by ground TSVs.

TABLE III

MAXIMUM VARIATION OF MAGNITUDE AND PHASE WITH RESPECT

TO THE NUMBER OF SURROUNDING GROUND TSVS

|             | Non-shield | Coaxially-shielded TSVs |       |       |       |       |

|-------------|------------|-------------------------|-------|-------|-------|-------|

|             | 1S 0G      | 1S 1G                   | 1S 2G | 1S 4G | 1S 6G | 1S 8G |

| Mag. (dB)   | 1.46       | 0.56                    | 0.46  | 0.32  | 0.21  | 0.08  |

| Phase (deg) | 14.42      | 13.88                   | 10.03 | 7.79  | 8.54  | 6.84  |

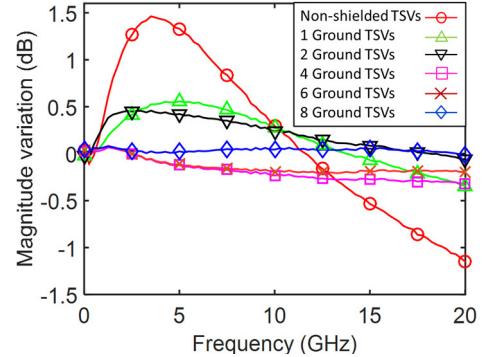

To quantitatively analyze this shielding effect with respect to the number of ground TSVs, five sets of shielded TSVs are measured, as summarized in Fig. 10 and Table III. First, the nonshielded TSVs are measured as a reference, showing a maximum magnitude difference of 1.46 dB between the silicon and microfluidic heat sink cases. It can be seen that the measurement variation reduces both in magnitude and phase as the number of ground TSVs increases. The results clearly indicate that the shielded TSVs with eight ground TSVs almost preserve TSV frequency response regardless of surrounding medium. However, as the number of ground TSVs increases, the allocation for copper in silicon increases. As discussed

(a)

(b)

Fig. 8. High-frequency measurement results. (a) Magnitude and (b) phase of  $S_{11}$  of coaxially shielded and nonshielded TSVs in silicon and DI water, respectively.

Fig. 9. Extracted capacitance and conductance from measurements for coaxially shielded and nonshielded TSVs.

in Section II, it is preferable to minimize the allocation of copper in a silicon substrate. Thus, it is critical to determine the optimal number of ground TSVs that provides sufficient shielding. In our measurements, four to six ground TSVs showed sufficient shielding.

#### IV. LOW-LOSS TSV TECHNOLOGY

To attain a significant reduction in TSV electrical loss, various approaches have been studied (as summarized in Table IV). Low- $k$  materials and increased liner thickness were proposed to reduce capacitance and loss [27]. To reduce substrate losses at a higher frequency range, high-resistivity silicon and glass substrates were proposed [27], [28]. Moreover, instead of changing an entire substrate, several

Fig. 10. Magnitude variation of nonshielded TSVs and shielded TSVs with different number (0, 1, 2, 4, 6, and 8) of ground TSVs.

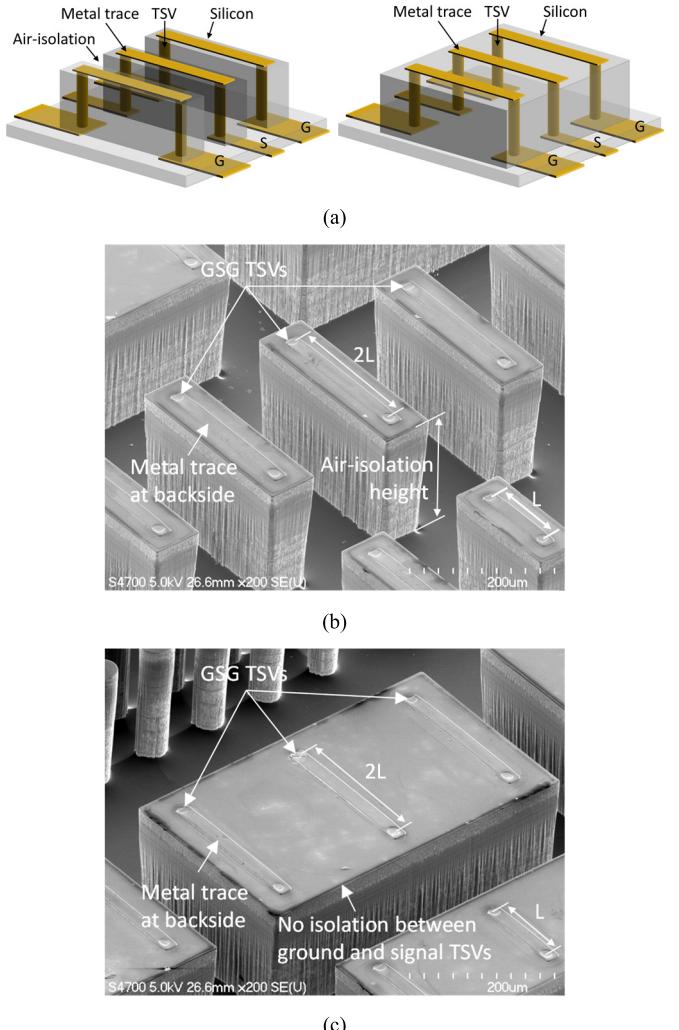

Fig. 11. (a) 3-D schematics of air-isolated TSV technology (left) and nonisolated TSVs (right) with a GSG configuration. SEM images of (b) air-isolated TSVs and (c) nonisolated TSVs. Etched silicon with back metal traces of a length of  $L$  and  $2L$ , respectively.

researchers have proposed the substitution of a localized silicon region with low-loss materials. One study proposed the formation of local polymer-wells with embedded TSVs in a silicon substrate [29]. In a similar manner, localized glass

TABLE IV

COMPARISON OF NONTRADITIONAL TSVs FOR ELECTRICAL LOSS REDUCTION IN THE LITERATURE

| Parameters         | P. Thadesar et al.<br>[29]        | J.-Y. Lee et al.<br>[30]                 | V. Sukumaran et al.<br>[28]                                          | M. Sunohara et al.<br>[31]                    | H. Oh et al.<br>[32]                       | C. Huang et al.<br>[33]               |

|--------------------|-----------------------------------|------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------|---------------------------------------|

| TSV diameter       | 65/100 $\mu\text{m}$              | 40 $\mu\text{m}$                         | 15 $\mu\text{m}$ (upper <sup>**</sup> )<br>7~8 $\mu\text{m}$ (lower) | 60 $\mu\text{m}$                              | 13 $\mu\text{m}$                           | 10/30 $\mu\text{m}$                   |

| TSV height         | 285 $\mu\text{m}$                 | 100 $\mu\text{m}$                        | 30 $\mu\text{m}$                                                     | 350 $\mu\text{m}$                             | 300 $\mu\text{m}$                          | 50 $\mu\text{m}$                      |

| TSV pitch          | 250 $\mu\text{m}$                 | 80/90/100 $\mu\text{m}$<br>(TSV spacing) | 27 $\mu\text{m}$                                                     | 200 $\mu\text{m}$                             | 100 $\mu\text{m}$                          | N/A                                   |

| Low-loss technique | Localized SU-8<br>into silicon    | Localized glass<br>into silicon          | Glass substrate                                                      | Air trench between<br>silicon and copper      | Air isolation in<br>silicon                | Air gap between<br>silicon and copper |

| Low-loss formation | SU-8 fill after<br>silicon etch   | Glass reflow after<br>silicon etch       | Glass substrate                                                      | Silicon etch<br>(width: 20~30 $\mu\text{m}$ ) | Silicon etch (width:<br>50 $\mu\text{m}$ ) | PPC <sup>*</sup>                      |

| Insertion loss     | ~1 dB<br>@ 50 GHz                 | ~0.4 dB<br>@ 50 GHz                      | ~0.1 dB<br>@ 20 GHz                                                  | ~6.2 dB<br>@ 40 GHz                           | ~0.5 dB<br>@ 20 GHz                        | N/A                                   |

| Characterization   | Total loss of GSG<br>TSVs and CPW | Total loss of GSG<br>TSVs and CPW        | Total loss of GSG<br>TSVs and CPW                                    | Total loss of GSG<br>TSVs and CPW             | De-embedded<br>single TSV loss             | DC capacitance<br>measurements        |

<sup>\*</sup>PPC stands for propylenecarbonate.

<sup>\*\*</sup>Tapered TSVs are shown with the dimension of 15  $\mu\text{m}$  at one end and 7~8  $\mu\text{m}$  at the other end.

Fig. 12. (a) Insertion loss of air-isolated and nonisolated TSVs for TSV pitches of 100 and 200  $\mu\text{m}$  after L-2L deembedding. (b) Extracted TSV capacitance. (c) TSV conductance from the measured scattering matrixes.

formation was demonstrated using glass reflow after partially etching a silicon substrate [30]. In addition, the formation of an air gap between copper and silicon was proposed using

propylenecarbonate [33] or air trench formation [31]. The permittivity of air is approximately 1, and thus it is most attractive to use air for loss reduction. However, the fabrication of an air liner or air gap between copper and silicon is considered challenging since it requires additional materials and fabrication steps.

To address such challenges, this section discusses low-loss TSVs achieved by simply etching silicon around the TSVs for silicon interposer applications [32]. This approach results in reduced loss, as well as capacitance of TSVs, while avoiding complex fabrication steps.

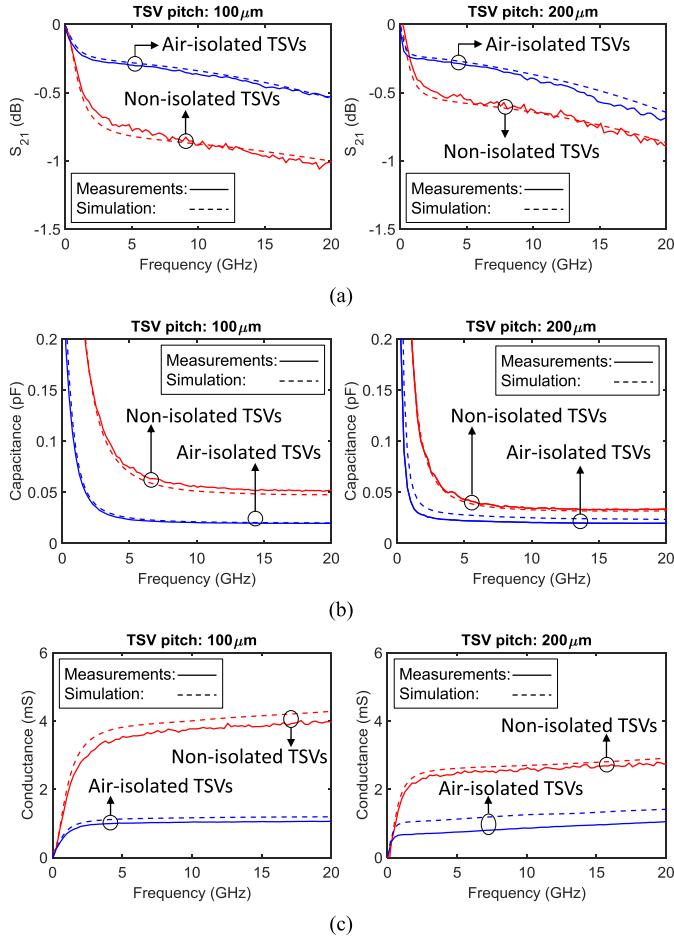

Fig. 11 presents the two types of GSG TSVs embedded in silicon pillars with 3-D layouts and SEM images. Fig. 11(b) shows air-isolated TSVs, where signal and ground TSVs are partially isolated using air. On the other hand, the GSG TSVs in Fig. 11(c) do not include any isolation between signal and ground TSVs, which we refer to as nonisolated TSVs. To investigate the reduction in insertion loss and TSV parasitics, the fabricated air-isolated and nonisolated TSVs are compared using high-frequency measurements and full-wave simulations. To extract single TSV loss from a TSV/trace-mixed structure, the L-2L deembedding technique [38] is performed using two lengths (L and 2L as shown in Fig. 11) of metal traces. The height and width of the air-isolation are 220 and 50  $\mu\text{m}$ , respectively. TSV diameter and height are 13 and 320  $\mu\text{m}$ , respectively, and TSV pitches of 100 and 200  $\mu\text{m}$  are used. Fig. 12 illustrates the insertion loss, extracted capacitance, and conductance of single TSV after L-2L deembedding. It shows approximately 50% and 30% reduction in insertion loss at 20 GHz for the TSV pitch of 100 and 200  $\mu\text{m}$ , respectively.

## V. CONCLUSION

This paper discusses the design considerations, fabrication, and high-frequency characterization of three types of nontraditional TSV technologies. First, TSVs integrated with

microfluidic cooling are discussed for thermally limited 3-D integrated microsystems. This paper investigates the impact of microfluidic designs on TSV electrical performance since the frequency-dependent permittivity of DI water significantly changes TSV electrical parasitics. The capacitance and conductance of TSVs increased by 104.4% and 121.3%, respectively. This implies that the design of microfluidic cooling is strongly correlated with electrical TSV performance, and vice versa. Second, coaxial TSV configurations were investigated to electrically shield signal transmission in TSVs. Coaxially shielded TSVs, in which multiple ground TSVs surround a signal TSV, successfully shielded signal TSVs from the impact of the surrounding DI water. While shielding improves as the number of ground TSV increases, it also increases the area allocation of copper in a silicon substrate. Thus, an optimal number of ground TSVs should be considered to satisfy shielding requirements, minimize silicon real estate, and lower manufacturing cost. Finally, low-loss TSV techniques were discussed for silicon interposer applications. While there are many loss-reduction techniques in the literature, air-isolation in a silicon substrate greatly reduces the electrical loss and capacitance of TSVs without increasing fabrication complexity.

#### ACKNOWLEDGMENT

The authors would like to thank technical staff with the Institution of Electronics and Nanotechnology (IEN), Georgia Tech. They would also like to thank Enthon for providing electroplating solutions and Cabot Microelectronics Corporation for providing CMP slurries.

#### REFERENCES

- [1] K. Kim, "Silicon technologies and solutions for the data-driven world," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 1–7.

- [2] M. Horowitz, "Computing's energy problem (and what we can do about it)," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 10–14.

- [3] T. Skotnicki *et al.*, "Innovative materials, devices, and CMOS technologies for low-power mobile multimedia," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 96–130, Jan. 2008.

- [4] L. A. Polka *et al.*, "Package technology to address the memory bandwidth challenge for terascale computing," *Intel Technol. J.*, vol. 11, no. 3, pp. 197–205, 2007.

- [5] M. S. Bakir and J. D. Meindl, Eds., *Integrated Interconnect Technologies for 3D Nanoelectronic Systems*. Norwood, MA, USA: Artech House, 2009.

- [6] J. U. Knickerbocker *et al.*, "System-on-package (SOP) technology, characterization and applications," in *Proc. 56th IEEE Electron. Compon. Technol. Conf. (ECTC)*, May/Jun. 2006, pp. 415–421.

- [7] T. Matthias, G. Kreindl, V. Dragoi, M. Wimplinger, and P. Lindner, "CMOS image sensor wafer-level packaging," in *Proc. 12th Int. Conf. Electron. Packag. Technol. High Density Packag.*, Aug. 2011, pp. 1–6.

- [8] S. Sukegawa *et al.*, "A 1/4-inch 8 Mpixel back-illuminated stacked CMOS image sensor," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 484–485.

- [9] D. U. Lee *et al.*, "A 1.2 V 8 Gb 8-channel 128 GB/s high-bandwidth memory (HBM) stacked DRAM with effective microbump I/O test methods using 29 nm process and TSV," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2014, pp. 432–433.

- [10] J.-S. Kim *et al.*, "A 1.2 V 12.8 GB/s 2 Gb mobile wide-I/O DRAM with 4×128 I/Os using TSV based stacking," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 107–116, Jan. 2012.

- [11] J. Jeddelloh and B. Keeth, "Hybrid memory cube new DRAM architecture increases density and performance," in *Proc. Symp. VLSI Technol. (VLSIT)*, 2012, pp. 87–88.

- [12] C. R. King, D. Sekar, M. S. Bakir, B. Dang, J. Pikarsky, and J. D. Meindl, "3D stacking of chips with electrical and microfluidic I/O interconnects," in *Proc. 58th Electron. Compon. Technol. Conf.*, 2008, pp. 1–7.

- [13] T. Sarvey *et al.*, "Embedded cooling technologies for densely integrated electronic systems," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2015, pp. 1–8.

- [14] L. Zheng, Y. Zhang, G. Huang, and M. S. Bakir, "Novel electrical and fluidic microbumps for silicon interposer and 3-D ICs," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 4, no. 5, pp. 777–785, May 2014.

- [15] Y. Madhour *et al.*, "Integration of intra chip stack fluidic cooling using thin-layer solder bonding," in *Proc. IEEE Int. 3D Syst. Integr. Conf. (3DIC)*, Oct. 2013, pp. 1–8.

- [16] Y. Zhang, A. Dembla, and M. S. Bakir, "Silicon micropin-fin heat sink with integrated TSVs for 3-D ICs: Tradeoff analysis and experimental testing," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 3, no. 11, pp. 1842–1850, Nov. 2013.

- [17] N. Khan *et al.*, "3-D packaging with through-silicon via (TSV) for electrical and fluidic interconnections," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 3, no. 2, pp. 221–228, Feb. 2013.

- [18] Y. Zhang, H. Oh, and M. S. Bakir, "Within-tier cooling and thermal isolation technologies for heterogeneous 3D ICs," in *Proc. IEEE Int. 3D Syst. Integr. Conf. (3DIC)*, Oct. 2013, pp. 1–6.

- [19] H. Oh, Y. Zhang, T. E. Sarvey, G. S. May, and M. S. Bakir, "TSVs embedded in a microfluidic heat sink: High-frequency characterization and thermal modeling," in *Proc. IEEE 20th Workshop Signal Power Integr. (SPI)*, May 2016, pp. 1–4.

- [20] P. Leduca *et al.*, "Challenges for 3D IC integration: Bonding quality and thermal management," in *Proc. IEEE Int. Interconnect Technol. Conf.*, Jun. 2007, pp. 210–212.

- [21] S. W. Ho, S. W. Yoon, Q. Zhou, K. Pasad, V. Kripesh, and J. H. Lau, "High RF performance TSV silicon carrier for high frequency application," in *Proc. 58th Electron. Compon. Technol. Conf.*, May 2008, pp. 1946–1952.

- [22] D. H. Jung *et al.*, "30 Gbps high-speed characterization and channel performance of coaxial through silicon via," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, no. 11, pp. 814–816, Nov. 2014.

- [23] J.-M. Yook, D. Kim, J.-C. Park, C.-Y. Kim, S. H. Yi, and J. C. Kim, "Low-loss and high-isolation through silicon via technology for high performance RF applications," in *Proc. 44th Eur. Microw. Conf.*, 2014, pp. 996–999.

- [24] P. A. Thadesar and M. S. Bakir, "Fabrication and characterization of mixed-signal polymer-enhanced silicon interposer featuring photodefined coax TSVs and high-Q inductors," in *Proc. IEEE 65th Electron. Compon. Technol. Conf. (ECTC)*, May 2015, pp. 281–286.

- [25] S. Adamshick, D. Coolbaugh, and M. Liehr, "Experimental characterization of coaxial through silicon vias for 3D integration," *Microelectron. J.*, vol. 46, no. 5, pp. 377–382, 2015.

- [26] H. Oh, X. Zhang, G. S. May, and M. S. Bakir, "High-frequency analysis of embedded microfluidic cooling within 3-D ICs using a TSV testbed," in *Proc. IEEE 66th Electron. Compon. Technol. Conf. (ECTC)*, May/Jun. 2016, pp. 68–73.

- [27] T. Bandyopadhyay, R. Chatterjee, D. Chung, M. Swaminathan, and R. Tummala, "Electrical modeling of through silicon and package vias," in *Proc. IEEE Int. Conf. 3D Syst. Integr.*, Sep. 2009, pp. 1–8.

- [28] V. Sukumaran *et al.*, "Design, fabrication, and characterization of ultrathin 3-D glass interposers with through-package-vias at same pitch as TSVs in silicon," *IEEE Compon., Packag., Manuf. Technol.*, vol. 4, no. 5, pp. 786–795, May 2014.

- [29] P. A. Thadesar and M. S. Bakir, "Novel photo-defined polymer-enhanced through-silicon vias for silicon interposers," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 3, no. 7, pp. 1130–1137, Jul. 2013.

- [30] J.-Y. Lee, S.-W. Lee, S.-K. Lee, and J.-H. Park, "Through-glass copper via using the glass reflow and seedless electroplating processes for wafer-level RF MEMS packaging," *J. Micromech. Microeng.*, vol. 23, no. 8, p. 085012, Aug. 2013.

- [31] M. Sunohara, H. Sakaguchi, A. Takano, R. Arai, K. Murayama, and M. Higashi, "Studies on electrical performance and thermal stress of a silicon interposer with TSVs," in *Proc. 60th Electron. Compon. Technol. Conf.*, 2010, pp. 1088–1093.

- [32] H. Oh, G. S. May, and M. S. Bakir, "Silicon interposer platform with low-loss through-silicon vias using air," in *Proc. Int. 3D Syst. Integr. Conf. (3DIC)*, vol. 2, 2015, pp. TS11.3.1–TS11.3.4.

- [33] C. Huang, Q. Chen, and Z. Wang, "Air-gap through-silicon vias," *IEEE Electron Device Lett.*, vol. 34, no. 3, pp. 441–443, Mar. 2013.

- [34] K. H. Lu, X. Zhang, S.-K. Ryu, J. Im, R. Huang, and P. S. Ho, "Thermomechanical reliability of 3-D ICs containing through silicon vias," in *Proc. IEEE 59th Electron. Compon. Technol. Conf. (ECTC)*, May 2009, pp. 630–634.

- [35] U. Kaatze, "Complex permittivity of water as a function of frequency and temperature," *J. Chem. Eng. Data*, vol. 34, no. 4, pp. 371–374, Oct. 1989.

- [36] I. Ndip *et al.*, "Analytical, numerical-, and measurement-based methods for extracting the electrical parameters of through silicon vias (TSVs)," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 4, no. 3, pp. 504–515, Mar. 2014.

- [37] Z. Xu and J.-Q. Lu, "Through-silicon-via fabrication technologies, passives extraction, and electrical modeling for 3-D integration/packaging," *IEEE Trans. Semicond. Manuf.*, vol. 26, no. 1, pp. 23–34, Feb. 2013.

- [38] H.-T. Yen *et al.*, "TSV RF de-embedding method and modeling for 3DIC," in *Proc. Annu. SEMI Adv. Semiconductor Manuf. Conf.*, 2012, pp. 394–397.

**Hanju Oh** (S'14) received the B.S. degree in electrical and computer engineering from Hanyang University, Seoul, South Korea, in 2010, and the M.S. degree from the Georgia Institute of Technology, Atlanta, GA, USA, in 2014, where he is currently pursuing the Ph.D. degree in electrical and computer engineering.

Mr. Oh was a recipient of the Best Oral Session Paper award of the IEEE Global Interposer Technology Workshop in 2014, the 2015 Charles Hutchins Educational Grant Award from the Surface Mount Technology Association and the *Circuits Assembly Magazine*, and the IEEE Electronic Components and Technology Conference in 2016, and a co-recipient of the Best Poster Award in the thermal track at Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems in 2014.

**Gary S. May** (S'85–M'90–SM'97–F'06) received the B.S. degree in electrical engineering from the Georgia Institute of Technology (Georgia Tech), Atlanta, GA, USA, in 1985, and the M.S. and Ph.D. degrees in electrical engineering and computer science from the University of California at Berkeley, Berkeley, CA, USA, in 1987 and 1991, respectively.

He was a member of the Technical Staff with AT&T Bell Laboratories, Murray Hill, NJ, USA. He was the Steve W. Chaddick School Chair with the School of Electrical and Computer Engineering, Georgia Tech, from 2005 to 2011, where he is currently the Dean with the College of Engineering. He serves as the Chief Academic Officer of the college and provides leadership to over 400 faculty members and over 13 000 students in the fourth-ranked engineering program in the nation. His current research interests include computer-aided manufacturing of integrated circuits, semiconductor process and equipment modeling, process simulation and control, automated process and equipment diagnosis, and yield modeling.

Dr. May is a Fellow of the American Association for the Advancement of Science and a member of the National Advisory Board of the National Society of Black Engineers. He was the Editor-in-Chief of the *IEEE TRANSACTIONS ON SEMICONDUCTOR MANUFACTURING* from 1997 to 2001, and was a National Science Foundation National Young Investigator from 1993 to 1998. He was a Graduate Fellow with the National Science Foundation and AT&T Bell Laboratories.

**Muhammed S. Bakir** (S'98–M03–SM'12) received the B.E.E. degree from Auburn University, Auburn, AL, USA, in 1999, and the M.S. and Ph.D. degrees in electrical and computer engineering from the Georgia Institute of Technology (Georgia Tech), Atlanta, GA, USA, in 2000 and 2003, respectively.

He is currently a Professor with the School of Electrical and Computer Engineering, Georgia Tech. His current research interests include 3-D electronic system integration, advanced cooling and power delivery for 3-D systems, biosensors and their integration with CMOS circuitry, and nanofabrication technology.

Dr. Bakir was a recipient of the 2013 Intel Early Career Faculty Honor Award, the 2012 DARPA Young Faculty Award, and the 2011 IEEE CPMT Society Outstanding Young Engineer Award, and was an invited participant in the 2012 National Academy of Engineering Frontiers of Engineering Symposium. He and his research group have received over 20 conference and student paper awards, including six from the IEEE Electronic Components and Technology Conference, four from the IEEE International Interconnect Technology Conference, and one from the IEEE Custom Integrated Circuits Conference. His group received the 2014 Best Paper of the *IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY* in the area of advanced packaging. In 2015, He was elected by the IEEE CPMT Society to serve as a Distinguished Lecturer and was an invited Speaker at the U.S. National Academies Frontiers of Sensor Science Symposium. He is an Editor of the *IEEE TRANSACTIONS ON ELECTRON DEVICES* and an Associate Editor of the *IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY*.